Лабораторный синтезатор СВЧ. Схема, описание

При разработке и налаживании СВЧ устройств у радиолюбителей часто возникают сложности, связанные с отсутствием измерительной аппаратуры нужного диапазона частот. Предлагаемый синтезатор частоты можно изготовить в любительских условиях. Он работает в диапазоне 1900...2275 МГц. Значение частоты выбирают из нескольких возможных с помощью переключателя.

На относительно низких частотах (до 100... 150 МГц) проблему стабилизации частоты генератора решают применением кварцевых резонаторов, на более высоких (400 МГц) - с помощью резонаторов на поверхностно-акустических волнах (ПАВ-резонаторов), на СВЧ используют диэлектрические резонаторы из высококачественной керамики и другие высокодобротные резонаторы. Стабилизация с помощью пассивных компонентов имеет свои достоинства - простоту и сравнительную дешевизну реализации. Ее главный недостаток состоит в невозможности существенного изменения частоты генерируемого сигнала без смены частотозадающего элемента.

Получившие широкое распространение интегральные синтезаторы частоты позволяют реализовать быструю электронную перестройку генератора (в том числе СВЧ), поддерживая при этом высокую стабильность частоты. Синтезаторы бывают прямого и косвенного типов.

Достоинствами прямого синтеза считают высокую скорость смены частоты и перестройку с малым шагом. Однако из-за присутствия в синтезированном сигнале большого числа спектральных компонент, возникших в результате многочисленных нелинейных преобразований, в СВЧ аппаратуре устройства прямого синтеза применяют редко.

Для синтеза СВЧ чаще применяют синтезаторы косвенного типа с фазовой

автоподстройкой частоты (ФАПЧ). Принцип функционирования ФАПЧ, а также методика

расчета фильтра обратной связи широко и неоднократно рассмотрены в литературе,

например, в . Существует несколько бесплатно распространяемых программ,

позволяющих рассчитать оптимальные параметры фильтров обратной связи, их можно

найти в Интернете на сайте

Интегральные синтезаторы с ФАПЧ бывают двух типов: программируемые (значения частоты задают внешними командами) и непрограммируемые (фиксированные коэффициенты умножения и деления образцовой частоты изменить невозможно).

К недостаткам непрограммируемых интегральных синтезаторов, например, МС12179, следует отнести необходимость применения кварцевого резонатора с точно заданной частотой, что не всегда возможно. Программируемые синтезаторы, например, UMA1020M, лишены этого недостатка. При наличии управляющего микроконтроллера настроить такой синтезатор на заданную частоту технически несложно. Необходимые для совместной работы с микросхемой-синтезатором автогенераторы СВЧ с электронной перестройкой частоты доступны потребителю в виде функционально законченных модулей, выполненных по гибридной технологии .

Схема лабораторного синтезатора частоты, предназначенного для проверки и

регулировки настройки аппаратуры диапазона 2 ГГц, показана на рис, 1. Его основа

- микросхема UMA-1020М (DA3), техническую документацию на которую можно найти на

Интернет-сайте ее производителя по адресу

В синтезаторе имеются также управлявмый напряжением генератор (ГУН) DA1, кварцевый генератор образцовой частоты 10 МГц DA2 и микроконтроллер DD1. СВЧ сигнал с выхода ГУН поступает на выход синтезатора (разъем XW1) и на вход главного программируемого делителя частоты микросхемы DA3. Сигнал образцовой частоты с выхода генератоpa DA2 поступает на вспомогательный программируемый делитель частоты, также входящий в состав микросхемы DA3.

Коэффициенты деления частоты главным и вспомогательным делителями задает микроконтроллер DD1 (Z86E0208PSC), посылая по трехпроводной информационной шине (выводы 11-13 DA3) соответствующие команды. Исходный текст управляющей программы приведен в табл. 1. Внутренней памяти микроконтроллера достаточно для хранения данных о семи различных значениях частоты. Одно из значений частоты или режим, в котором сигнал на выходе отсутствует, выбирают перемычками S1-S3 согласно табл. 2. Установленный режим вступает в силу в момент включения питания прибора, после чего никакие манипуляции с выключателями на его работу не влияют до нового включения. Светодиод HL1 должен погаснуть через 1 с после включения питания. О программировании микроконтроллеров фирмы Zilog можно прочитать в .

Синтезатор собран на печатной плате, внешний вид которой показан на рис. 2. Применены резисторы и конденсаторы для поверхностного монтажа.

Литература

- Стариков О. Метод ФАПЧ и принципы синтезирования высокочастотных сигналов. - Chip News, 2001, № 6.

- VCO Designer"s Handbook 2001. VCO/HB-01. - Mini-Circuits.

- Глвдштейн M. А. Микроконтроллеры семействаZ86 фирмы Zilog. Руководство программиста. - М.: ДОДЭКА, 1999, 96 с.

Кроме синтезатора СВЧ, микросхема UMA1020M содержит еще один, работающий в диапазоне частот 20..300 МГц, В описанной конструкции 6н не использован.

Бабковский А. П., Селезнев Н. Е. ФГУП НИИ измерительных систем им. Ю. Е. Седакова ГСП-486, Н. Новгород – 603950, Россия тел.: 8312-666202, доб.295, e-mail: [email protected]

Аннотация – Представлены результаты работы по проектированию простого СВЧ-синтезатора на С-диапазона на основе однокристальной микросхемы фазовой автоматической подстройки частоты.

I. Введение

Повышение рабочих частот до миллиметрового диапазона волн в устройствах ближней радиолокации с доплеровской обработкой отраженных сигналов требует значительного повышения стабильности излучаемых колебаний.

Использование схем обработки сигналов на основе измерения доплеровского смещения на промежуточных частотах в дециметровом диапазоне частот для получения максимальной эффективности работы устройства вынуждает использовать когерентные генераторы в тракте передатчика и приемного устройства.

В настоящий момент наиболее оптимальным способом получения когерентных сигналов для таких систем миллиметрового диапазона является использование синтезаторов частоты сантиметрового диапазона частот и последующего их умножения и усиления.

Как правило, такие синтезаторы строятся по многопетлевым схемам с использованием смесителей, делителей и умножителей частоты.

Однако, в последние годы верхняя рабочая частота однокристальных микросхем синтезаторов с фазовой автоматической подстройкой частоты (phase locked loop – PLL) поднялась до середины С- диапазона.

В настоящее время лидерами в производстве однокристальных микросхем PLL синтезаторов на этот диапазон частот являются компании Skyworks и Analog Devices.

На российском рынке электронных компонентов продукцию фирмы Skyworks Inc. представляет компания: ООО «Радиокомп» г. Москва .

С 1993 года после подписания прямого лицензионного соглашения с фирмой Analog Devices ЗАО «Аргуссофт Компани» г.Москва регулярно обновляет и предлагает разработчикам полный спектр компонентов и отладочных устройств.

Компания «МЭЙ Электронные компоненты» г. Москва представляет разработчикам подробные материалы по применению микросхем PLL синтезаторов разных производителей.

Повышение верхней рабочей частоты PLL синтезаторов до частот С-диапазона сделало возможным создавать достаточно простые по структуре однопетлевые синтезаторы.

В ряде случаев такой подход к построению задающего генератора (ЗГ) и гетеродинов является более выгодным с точки зрения технических, массо- габаритных и экономических показателей.

Основные параметры некоторых микросхем PLL синтезаторов, работающих в С-диапазоне, приведены в таблице 1.

Табл. 1. Сравнительные характеристики микросхем PLL синтезаторов.

Table 1. Comparison characteristics of PLL synthesizers’ ICs

II. Основная часть

Функциональная схема ЗГ и гетеродина такого типа на основе однопетлевого синтезатора частоты представлена на рисунке 1.

Рис.1. Структурная схема синтезатора.

Fig. 1 Synthesizer block diagram

где Ref. Gen. – прецизионный малошумящий опорный кварцевый генератор ГК62-ТС, рС – микроконтроллер, PLL IC – микросхема синтезатора, LPF – фильтр нижних частот, Scaling amplifier – масштабирующий операционный усилитель, Dielectric Resonator VCO – генератор управляемый напряжением (ГУН) на основе диэлектрического резонатора, Isolator – СВЧ-вентиль, Directional Coupler – направленный ответвитель.

Учитывая собственный опыт разработки СВЧ- синтезаторов и результаты исследования различных микросхем PLL синтезаторов, для разработки ЗГ и гетеродина выбрана микросхема СХ72302 с дробным переменным коэффициентом деления компании Skyworks Inc. .

Основные характеристики микросхемы СХ72302:

■ максимальная выходная частота основного канала – 6,1 ГГц;

■ вспомогательного – 1000 МГц;

■ предельная рабочая ИЧФД – 25 МГц;

■ гарантированное время переключения частоты не более 100 мкс;

■ уровень собственных шумов -128 дБ/Гц;

■ шаг перестройки частоты менее 400 Гц.

Применение СХ72302 позволяет при достаточно

высокой рабочей частоте импульсного частотнофазового детектора (ИЧФД) F=16,384 МГц получить шаг перестройки частоты 250 Гц за счет высокой степени дробности (262144). Повышение рабочей частоты ИЧФД приводит к снижению коэффициента умножения частоты петлей ФАПЧ и улучшению шумовых параметров сигнала.

Для снижения уровня шумов в выходном сигнале, используется генератор с высокодобротным диэлектрическим резонатором (ДР). Линейная перестройка частоты в таком генераторе осуществляется с помощью варикапа ЗА627А-6 слабо связанного с ДР. Использование транзистора 2Т963А-2 позволяет получить выходную мощность генератора порядка 50 мВт.

СВЧ-сигнал с выхода ГУНа поступает через вентиль и направленный ответвитель на выход синтезатора частоты (выходная мощность составляет + 15дБм – около 30 мВт). Часть мощности с направленного ответвителя (переходное ослабление 25 дБ) ответвляется на вход микросхемы PLL.

Параметры фильтра нижних частот в цепи обратной связи петли ФАПЧ были рассчитаны по методике компании National Semiconductor. В программе Math- CAD2000 была промоделирована работа петли ФАПЧ и проверена ее устойчивость в рабочем диапазоне частот.

При выходных частотах синтезатора в середине С-диапазона коэффициент умножения частоты петлей ФАПЧ достигает 380 (рабочая частота фазового детектора 16 МГц). Спектральная плотность фазовых шумов опорного кварцевого генератора ГК-62ТС-

0 составляет минус (145 – 155) дБ/Гц. Спектральная плотность фазовых шумов микросхемы PLL составляет 128 дБ/Гц. Поэтому, спектральная плотность фазовых шумов формируемого сигнала определяется микросхемой и составляет

Уф = -128+ 20 log 380 = -77 дБ/Гц.

Управление выходной частотой синтезатора осуществляется с помощью микроконтроллера AT90S8515-8PI Atmel . Для ускорения переходного процесса, переключение частот производится при максимальном токе фазового детектора. После захвата заданной частоты, ток фазового детектора снижается до номинального уровня, что приводит к снижению уровня дискретной составляющей с частотой сравнения фазового детектора в спектре выходного сигнала синтезатора. После переключения синтезатора микроконтроллер переходит в «спящий» режим с выключением своего кварцевого генератора для уменьшения шумов от цифровой части схемы.

Конструктивно синтезатор выполнен в виде набора отдельных узлов, соединенных между собой жесткими коаксиальными кабелями. Для микросхемы PLL и сопутствующей обвязки использована печатная плата из стеклотекстолита марки FR-4 толщиной 0,8 мм. Несмотря на сравнительно высокую рабочую частоту использование подложки из недорогого материала вполне оправдано.

III. Эксперимент

Были проведены экспериментальные исследования шумовых параметров синтезатора частоты с помощью установки для определения спектральной плотности фазовых шумов НР3048А.

Спектральная плотность фазовых шумов рассматриваемого простого однопетлевого синтезатора частоты при больших отстройках от несущей составляет:

10 кГц -92 дБ/Гц;

100 кГц -117 дБ/Гц.

Из-за слабой связи варикапа с диэлектрическим резонатором удалось получить достаточно неплохие шумовые параметры синтезатора, однако его полоса перестройки не превышает 50 МГц при изменении управляющего напряжения на варикапе от 1 до 25 В.

Для расширения рабочего диапазона частот синтезатора можно применить управляемый генератор на основе ЖИГ. Но при этом потребуется изменить схему управления частотой.

IV. Заключение

Применение однокристальной микросхемы с дробным коэффициентом деления в цепи обратной связи петли ФАПЧ позволяет конструировать компактные синтезаторы частоты по однопетлевой схеме с выходными частотами вплоть до верхней рабочей частоты микросхемы PLL при шаге перестройки по частоте в такой однопетлевой системе менее 400 Гц и приемлемом уровне спектральной плотности фазовых шумов.

V. Список литературы

ВЧ и СВЧ Радиокомпоненты зарубежных производителей. Прайс-лист. Выпуск 5. М. 2004г.

Www.argussoft.ru

«МЭЙ Электронные компоненты» Лето’2004.

ВЧ/СВЧ компоненты, электромеханика, силовые приборы. Электронный каталог 2004 г.

Бабковский А. П. Опыт проектирования PLL синтезаторов на микросхемах фирм QUALCOMM и Mini- Circuits для блока эталонных сигналов уровнемера миллиметрового диапазона. – В кн. «8-я Международная крымская конференция «СВЧ техника и коммуникационные технологии». Материалы конференции» [Севастополь, 14-17 сент. 1998 г.]. Севастополь: Вебер, 1998, т. 2, стр. 667-668.

Бабковский А. П., Селезнев Н. Е. Гибридные PLL/DDS синтезаторы частоты. – В кн. «11-я Международная крымская конференция «СВЧ техника и коммуникационные технологии». Материалы конференции» [Севастополь, 10-14 сент. 2001 г.]. Севастополь: Вебер, 2001, стр. 112-114.

Бабковский А. П., Селезнев Н. Е. Быстродействующий октавный синтезатор СВЧ- диапазона с малым шагом перестройки частоты. – В кн. «13-я Международная крымская конференция «СВЧ техника и коммуникационные технологии». Материалы конференции» [Севастополь, 8-12 сент. 2003 г.]. Севастополь: Вебер, 2003, стр. 136-138.

Www.skyworksinc.com

SINGLE-LOOP SYNTHESIZER FOR C-BAND WITH ULTRA FINE FREQUENCY STEP

Babkovsky A., Seleznev N.

Federal State Owned Unitary Enterprise Measuring Systems Research Institute names after Yu. Ye. Sedakov GSP-486, Nizhny Novgorod – 603950, Russia e-mail: [email protected]

Abstract – Considered in this paper are results of C-band simple frequency synthesizer design on the basis of single loop PLL.

Rising of operating frequencies of a short range Doppler radar up to MM-band demands a great improvement of transmitted signal stability.

The principle of signal processing is based on the reflected signals Doppler frequency measurement at the intermediate frequency (in UHF range). Thus the transmitter chain exciter and the receiver local oscillator (LO) must be coherent.

At present the most preferred approach in coherent signals generation is the use the C-band frequency synthesizers along with multipliers and amplifiers.

Frequently those synthesizers are designed using multiloop schematic in conjunction with frequency mixers, dividers and multipliers.

During the last years the PLL IC’s upper operating frequency was increased up to C-band. Now the leader manufacturers of the PLL IC’s for this frequency band are Skyworks and Analog Devices. Increase of IC operating frequency allows to design simple C-band single-loop frequency synthesizers.

In some cases this approach may is more preferable.

The block diagram of the transmitter exciter on the basis of single-loop PLL is shown in Fig.1. Taking into account our skills in synthesizer design, Skyworks CX72302 Fractional-N PLL IC was chosen for the exciter and LO design. For more details visit www.skyworksinc.com website.

Using CX72302 we can get 250Hz frequency step only with phase detector comparison frequency value 16.384MHz due to the high grade fractionality, 2 18 . High phase detector frequency leads to decrease of the main divider value N and noise parameters improvement.

High-Q dielectric resonator oscillator (DRO) is used for obtaining better noise performance out of PLL passband. Linear frequency sweep is carried out using a varicap having weak coupling with DR. The output power of DRO generator is 50 mW.

The signal passes through the isolator and directional coupler to the synthesizer output (output power is +15dBm – approx. 30 mW). A part of the power from the coupled port of the directional coupler is directed to the PLL IC input.

The loop filter components were calculated by the methods proposed by National Semiconductor. Loop stability analysis was evaluated in MathCAD 2000.

The main loop division ratio is increased up to 380 (phase detector frequency 16 MHz) at the frequencies about 6GHz. Phase noise spectral density of the PLL IC is -128 dB/Hz. Thus the phase noise spectral density in the PLL passband is determined by PLL IC noise, although the phase noise of the reference generator is (-145…-155 dB/Hz) and equal to -77dB/Hz.

Control of the synthesizer output frequency is carried out by Atmel AT90S8515-8PI microcontroller. In order to minimize the frequency switching time, the charge pump current is increased to its maximum value. After locking the charge pump current is switched to the nominal value and microcontroller is switched over to the sleep mode along with clock generator turning off. This allows to suppress noise in the output spectrum of the digital circuitry.

Noise parameters of the synthesizer output signal were measured by HP3048A test set.

Phase noise floor of the tested single-loop PLL synthesizer within offsets from the carrier is:

Frequency offset Phase noise floor

10 kHz -92 dB/Hz

100 kHz -117 dB/Hz

The weak coupling between the varicap and dielectric resonator in the tuned generator provides noise parameters rather good but the synthesized frequency band is too narrow (approximately 50 MHz within varicap tuning range from 1 to 25 volts).

It is possible to use YIG tuned oscillator to extend the synthesized frequency band. But in this case the frequency tuning circuitry must be changed.

Single chip Fractional-N PLL allows to construct small size single-loop frequency synthesizers for the frequencies up to the maximum operating PLL IC frequency with the frequency step less than 400 Hz and acceptable phase noise level.

Владельцы патента RU 2580068:

Изобретение относится к радиотехнике и может быть использовано в приемопередающих устройствах СВЧ диапазона частот. Техническим результатом является повышение устойчивой работы при перестройке частоты входного СВЧ сигнала. СВЧ синтезатор частот содержит СВЧ генератор, управляемый напряжением (ГУН), направленный ответвитель, СВЧ смеситель, источник входного СВЧ сигнала, первый делитель частоты с переменным коэффициентом деления, частотно-фазовый детектор, второй делитель частоты с переменным коэффициентом деления, источник опорного сигнала, фильтр нижних частот, фазовый компаратор, ждущий мультивибратор, два диода и операционный усилитель. 4 ил.

Изобретение относится к радиотехнике, а именно к широкодиапазонным СВЧ синтезаторам частот с предварительной, начальной, установкой частоты СВЧ генератора управляемого напряжением (ГУН), включенного в широкодиапазонную систему фазовой автоподстройки частоты (ФАПЧ) СВЧ синтезатора частот и может быть использовано в приемопередающих устройствах СВЧ диапазона частот.

Известны системы активного синтеза частот, в которых фильтрация колебаний синтезируемых частот осуществляется с помощью активного фильтра в виде петли фазовой автоподстройки частоты . При этом частота сигнала преобразуется, например, с помощью деления в низкочастотный диапазон, где происходит ее сравнение с частотой опорного генератора и вырабатывается напряжение автоподстройки СВЧ генератора, управляемого напряжением (ГУН). Системы активного синтеза обеспечивают более высокое подавление побочных спектральных составляющих и фазовых шумов несущего колебания. Однако в этой схеме за счет высокого коэффициента деления частоты ГУН нельзя достигнуть низкого уровня шумов выходного сигнала синтезатора.

Известен СВЧ синтезатор частот, реализующий принцип активного синтеза с петлей ФАПЧ, который выбран в качестве прототипа предлагаемого изобретения . СВЧ синтезатор частот содержит СВЧ ГУН, выход которого соединен через направленный ответвитель с выходом СВЧ синтезатора частот и с первым входом СВЧ смесителя, второй вход которого соединен с выходом источника входного СВЧ сигнала с частотой f вх СВЧ, выход СВЧ смесителя соединен с входом первого делителя частоты (ДЧ) с переменным коэффициентом деления n, выход которого соединен с первым входом частотно-фазового детектора (ЧФД), второй вход частотно-фазового детектора соединен с выходом второго делителя частоты с переменным коэффициентом деления m, вход которого соединен с источником опорного сигнала частоты f ОП, а выход частотно-фазового детектора через фильтр нижних частот (ФНЧ) соединен с входом СВЧ ГУН. При этом направленный ответвитель, смеситель, первый делитель частоты, ЧФД и ФНЧ образуют петлю ФАПЧ.

Известный СВЧ синтезатор частот обеспечивает возможность достижения низкого уровня фазовых шумов выходного сигнала СВЧ синтезатора частот с частотой f СЧ за счет уменьшения коэффициента деления первого делителя частоты при использовании в качестве входного СВЧ сигнала с частотой f вх СВЧ сигнала с низким уровнем фазовых шумов. Кроме того, уменьшение коэффициента деления первого делителя частоты позволяет увеличить коэффициент усиления петли ФАПЧ. Так как в такой схеме частота входного СВЧ сигнала f вх СВЧ выбирается из условия f вх СВЧ >f СЧ, то для поддержания постоянной величины коэффициента усиления петли ФАПЧ СВЧ синтезатора частот необходимо компенсировать изменение коэффициента деления первого делителя частоты изменением крутизны перестройки частоты СВЧ ГУН для сохранения полосы регулирования петли ФАПЧ.

Однако если уходы частоты f ГУH СВЧ ГУН будут более 2 f ПЧ (где промежуточная частота f ПЧ = f вх СВЧ -f ГУН), то в данном СВЧ синтезаторе частот будут происходить срывы фазовой синхронизации, что приведет к потере работоспособности синтезатора.

Кроме того, известный СВЧ синтезатор частот работает только в случае подачи на второй вход СВЧ смесителя входного СВЧ сигнала с фиксированной частотой f вх СВЧ. При подаче на этот вход СВЧ смесителя входного СВЧ сигнала с изменяемой (перестраиваемой) частотой f вх СВЧ в полосе, большей или равной 2 f ПЧ, в СВЧ синтезаторе частот также могут происходить нарушения фазовой синхронизации.

Технической задачей предлагаемого изобретения является создание широкодиапазонного СВЧ синтезатора частот с низким уровнем фазовых шумов и малым временем перестройки частоты выходного сигнала синтезатора f СЧ, обеспечивающим отсутствие нарушений фазовой синхронизации при изменении (перестройке) частоты входного СВЧ сигнала f вх СВЧ в полосе, равной или большей чем удвоенная частота сигнала промежуточной частоты f ПЧ, где f ПЧ = f вх СВЧ -f ГУН, а также обеспечивающего сохранение фазовой синхронизации при уходах частоты f ГУН сигнала СВЧ ГУН на величину более чем 2 f ПЧ.

Техническим результатом является предотвращение нарушений фазовой синхронизации, вызванных переходными процессами в петле ФАПЧ, и обеспечение устойчивой работы СВЧ синтезатора частот при эксплуатации, в том числе при перестройке частоты f вх СВЧ входного СВЧ сигнала

Сущность технического решения заключается в том, что предлагаемый СВЧ синтезатор частот содержит СВЧ генератор, управляемый напряжением (ГУН), выход которого соединен с входом направленного ответвителя, первый выход которого является выходом СВЧ синтезатора частот, а второй выход направленного ответвителя соединен с первым входом СВЧ смесителя, второй вход СВЧ смесителя соединен с выходом источника входного СВЧ сигнала, выход СВЧ смесителя соединен с входом первого делителя частоты с переменным коэффициентом деления, выход которого соединен с первым входом частотно-фазового детектора, второй вход частотно-фазового детектора соединен с выходом второго делителя частоты с переменным коэффициентом деления, вход которого соединен с выходом источника опорного сигнала, а между частотно-фазовым детектором и СВЧ ГУН включен фильтр нижних частот. СВЧ синтезатор частот дополнительно содержит фазовый компаратор, ждущий мультивибратор, два диода и операционный усилитель. При этом первый и второй выходы частотно-фазового детектора соединены соответственно с первым и вторым входами операционного усилителя, выход которого соединен с входом СВЧ ГУН, а фильтр нижних частот включен между первым входом операционного усилителя и его выходом, первый вход фазового компаратора соединен с выходом первого делителя частоты с переменным коэффициентом деления и первым входом частотно-фазового детектора, второй вход фазового компаратора соединен с выходом второго делителя частоты с переменным коэффициентом деления и со вторым входом частотно-фазового детектора, выход фазового компаратора соединен с входом ждущего мультивибратора, первый выход ждущего мультивибратора соединен через первый диод с первым выходом частотно-фазового детектора и с первым входом операционного усилителя, второй выход ждущего мультивибратора соединен через второй диод со вторым выходом частотно-фазового детектора и со вторым входом операционного усилителя. Причем первый и второй диоды включены встречно друг другу, при этом СВЧ ГУН, направленный ответвитель, СВЧ смеситель, первый делитель частоты, частотно-фазовый детектор, операционный усилитель и фильтр нижних частот образуют петлю фазовой автоподстройки частоты (ФАПЧ) при условии: Т М -τ м >τ ФАПЧ, где Т М - период колебаний ждущего мультивибратора, τ ФАПЧ - время установления синхронизации в петле фазовой автоподстройки частоты.

Включение в схему синтезатора СВЧ частот фазового компаратора и ждущего мультивибратора с двумя встречно включенными диодами на выходе позволяет проводить предварительную установку частоты f ГУН сигнала СВЧ ГУН при нарушении фазовой синхронизации в петле ФАПЧ, которые происходят при переключении частоты f вх СВЧ входного СВЧ сигнала или при уходах частоты f ГУН сигнала СВЧ ГУН, например, при включении СВЧ синтезатора, что обеспечивает быстрое восстановление фазовой синхронизации и повышает устойчивость работы СВЧ синтезатора частот. При этом после восстановления петли ФАПЧ ждущий мультивибратор отключается и не влияет на дальнейшую работу петли ФАПЧ.

Операционный усилитель с фильтром нижних частот в цепи обратной связи формирует полосу частот регулирования петли ФАПЧ.

Время между окончанием первого импульса и началом следующего импульса ждущего мультивибратора, определяемый RC-цепочкой этого мультивибратора, должно быть больше времени установления синхронизации в петле ФАПЧ, то есть должно выполняться условие:

Т М -τ м >τ ФАПЧ.

Изобретение поясняется чертежами.

На фиг. 1 представлена структурная схема предлагаемого СВЧ синтезатора частот, где

1 - СВЧ генератор (ГУН) с частотой f ГУН (управляющее напряжение U УПР);

3 - СВЧ смеситель;

4 - источник входного СВЧ сигнала с частотой f вх СВЧ;

5 - первый делитель частоты с переменным коэффициентом деления n;

6 - частотно-фазовый детектор (выходное напряжение U ЧФД);

7 - второй делитель частоты с переменным коэффициентом деления m;

8 - источник опорного сигнала с частотой f ОП;

9 - операционный усилитель;

10 - фильтр нижних частот;

11 - фазовый компаратор (выходное напряжение U ФК);

12 - ждущий мультивибратор (выходное напряжение прямое U м1 и инверсное

13 - первый диод;

14 - второй диод;

f ПЧ =f вх СВЧ -f ГУН - сигнал промежуточной частоты;

f СЧ - выходной сигнал СВЧ синтезатора частот.

На фиг. 2 представлены временные диаграммы входного U ФК и выходных U м1 и U м2 напряжений ждущего мультивибратора, входящего в состав предлагаемого СВЧ синтезатора частот, где

Т М - период колебаний ждущего мультивибратора 12;

τ м - длительность импульса ждущего мультивибратора 12;

τ ФАПЧ - время установления синхронизации в петле фазовой автоподстройки частоты.

На фиг. 3 показана полоса перестройки выходного СВЧ сигнала с частотой f СЧ =f ГУН относительно фиксированной частоты f вх СВЧ входного СВЧ сигнала предлагаемого СВЧ синтезатора частот.

На фиг. 4 показана полоса перестройки выходного СВЧ сигнала с частотой f СЧ =f ГУН относительно перестраиваемой частоты f вх СВЧ входного СВЧ сигнала предлагаемого СВЧ синтезатора частот.

Предлагаемый СВЧ синтезатор частот, структурная схема которого изображена на фиг. 1, содержит СВЧ генератор управляемый напряжением (ГУН) 1, выход которого соединен с входом направленного ответвителя 2, один выход которого является выходом СВЧ синтезатора частот, а другой выход направленного ответвителя 2 соединен с первым входом СВЧ смесителя 3, второй вход которого соединен с выходом источника входного СВЧ сигнала 4 с частотой f вх СВЧ. Выход СВЧ смесителя 3 соединен с входом первого делителя частоты 5 с переменным коэффициентом деления n, выход которого соединен с первым входом частотно-фазового детектора 6. Второй вход частотно-фазового детектора 6 соединен с выходом второго делителя частоты 7 с переменным коэффициентом деления m, вход которого соединен с выходом источника опорного сигнала 8 с частотой f ОП. Два выхода частотно-фазового детектора 6 соединены с двумя входами операционного усилителя 9, выход которого соединен с входом генератора СВЧ ГУН 1, при этом между первым входом операционного усилителя 9 и его выходом включен фильтр нижних частот 10. Первый вход дополнительно введенного в схему фазового компаратора 11 соединен с выходом первого делителя частоты 5 и первым входом частотно-фазового детектора 6, второй вход фазового компаратора 11 соединен с выходом второго делителя частоты 7 и вторым входом частотно-фазового детектора 6. Выход фазового компаратора 11 соединен с входом ждущего мультивибратора 12, прямой выход которого через первый диод 13 соединен с первым выходом частотно-фазового детектора бис первым входом операционного усилителя 9, инверсный выход ждущего мультивибратора 12 через второй диод 14 соединен со вторым выходом частотно-фазового детектора 6 и со вторым входом операционного усилителя 9, причем первый и второй диоды включены встречно друг другу. В данной схеме СВЧ ГУН 1, направленный ответвитель 2, СВЧ смеситель 3, первый делитель частоты 5, частотно-фазовый детектор 6, второй делитель частоты 7, операционный усилитель 9 и фильтр нижних частот 10 образуют петлю ФАПЧ.

Предлагаемый СВЧ синтезатор частот работает следующим образом. Выходной сигнал СВЧ ГУН 1 с частотой f ГУН через ответвитель 2 и выходной СВЧ сигнал источника входного СВЧ сигнала 4 с частотой f вх СВЧ поступают на СВЧ смеситель 3, на выходе которого выделяется сигнал промежуточной частоты f ПЧ, который поступает на вход первого делителя частоты 5 и после деления на коэффициент n сигнал с выхода первого делителя частоты 5 поступает на первый вход частотно-фазового детектора 6. Сигнал опорной частоты f ОП с выхода источника опорного сигнала 8 поступает на вход второго делителя частоты 7, где происходит деление частоты на коэффициент m. Сигнал с выхода второго делителя частоты 7 поступает на второй вход частотно-фазового детектора (ЧФД) 6, в котором он сравнивается с сигналом, поступившим с выхода первого делителя частоты 5, и на двух выходах частотно-фазового детектора 6 вырабатывается управляющее напряжение U ЧФД, величина и знак которого пропорциональны разности частот и фаз сравниваемых сигналов. Это управляющее напряжение U ЧФД через операционный усилитель 9 и фильтр нижних частот 10, включенный в цепь обратной связи операционного усилителя 9, подается на управляющий вход СВЧ ГУН 1 как управляющее напряжение U УПР., выполняя непрерывную подстройку частоты СВЧ ГУН 1, влияющую на режим фазовой синхронизации в петле ФАПЧ.

Условиями выполнения частотно-фазовой синхронизации в петле ФАПЧ являются равенство частот и фаз сигналов, подаваемых на входы частотно-фазового детектора, то есть f ОП /m=f ПЧ /n, φ ОП =φ ПЧ,

где f ПЧ = f вх СВЧ -f ГУН,

m - коэффициент деления частоты опорного сигнала с частотой f ОП;

n - коэффициент деления частоты сигнала промежуточной частоты f ПЧ;

φ ОП - фаза опорного сигнала с частотой f ОП;

φ ПЧ - фаза сигнала промежуточной частоты f ПЧ.

При перестройке частоты входного СВЧ сигнала f вх СВЧ в полосе, равной или большей чем удвоенная частота сигнала промежуточной частоты f ПЧ, где f ПЧ =f вх СВЧ -f ГУН, а также при уходах частоты сигнала СВЧ ГУН f ГУН на величину более чем 2 f ПЧ, входной СВЧ сигнал f вх СВЧ в предлагаемом изобретении проходит через петлю ФАПЧ СВЧ синтезатора частот, то есть через фазовый компаратор 11, ждущий мультивибратор 12, а также встречно включенные диоды 13, 14.

При наличии фазовой синхронизации в петле ФАПЧ с выхода фазового компаратора 11 на ждущий мультивибратор 12 поступает управляющий сигнал, отключающий ждущий мультивибратор 12, то есть выходное напряжение фазового компаратора 11 U ФК (например, уровня транзисторно-транзисторной логики ТТЛ) в виде логической единицы. В это время ждущий мультивибратор 12 не вырабатывает на прямом и инверсном выходах импульсных выходных сигналов с напряжениями соответственно U М1 , U М2 и не влияет на работу петли ФАПЧ. На прямом и инверсном выходах ждущего мультивибратора 12 противофазно устанавливаются постоянные напряжения U М1 и U М2 , соответствующие логическому нулю и логической единице). Временные диаграммы входного U ФК и выходных U М1 и U М2 напряжений ждущего мультивибратора 12 показаны на фиг. 2

При нарушении синхронизации частоты и фазы в петле ФАПЧ сигнал U ФК в виде логического нуля с выхода фазового компаратора 11 запускает ждущий мультивибратор 12, который на прямом и инверсном выходах вырабатывает выходные импульсные сигналы с напряжениями U М1 (соответствующий логической единице) и U М2 (соответствующий логическому нулю), поступающие через диоды 13, 14 соответственно на первый и второй входы операционного усилителя 9. Во время действия импульса ждущего мультивибратора 12, то есть в течение длительности τ м импульса ждущего мультивибратора 12, в зависимости от фазировки входов ЧФД 6, на выходе операционного усилителя 9 устанавливается максимальное или минимальное значение напряжения управления частотой сигнала СВЧ ГУН 1. В этом случае нарушаются условия частотно-фазовой синхронизации (f ОП /m=f ПЧ /n, φ ОП =φ ПЧ) и частотно-фазовый детектор 6 вырабатывает управляющее напряжение U ЧФД, которое обеспечивает восстановление синхронизации (то есть запуск процесса синхронизации) в петле ФАПЧ. При восстановлении частотно-фазовой синхронизации в петле ФАПЧ фазовый компаратор 11 отключает ждущий мультивибратор 12 (на его выходах снова противофазно устанавливаются постоянные напряжения, соответствующие логическому нулю и логической единице). В случае повторного нарушения частотно-фазовой синхронизации в петле ФАПЧ или в случае сбоя в работе петли ФАПЧ фазовый компаратор 11 вновь запускает ждущий мультивибратор 12 и весь процесс восстановления синхронизации повторяется.

В ряде случаев для работы петли ФАПЧ, исключающей нарушение в ней частотно-фазового синхронизации, необходимо, чтобы переходной процесс перестройки частоты СВЧ ГУН в петле ФАПЧ начинался от нижнего (f ГУН мин) или верхнего (f ГУН макс) края рабочего диапазона СВЧ ГУН к точке захвата частоты, в которой f ГУН =f СЧ, то есть начальный уровень напряжения, поступающего на управляющий вход СВЧ ГУН 1 (в режиме переходного процесса, предшествующего захвату частоты), всегда равнялся минимальному или максимальному значению. Это определяется положением частоты f ГУН выходного сигнала СВЧ ГУН относительно частоты f вх СВЧ входного СВЧ сигнала. При этом возможны два основных режима работы СВЧ синтезатора частот, при которых возможно нарушения синхронизации в петле ФАПЧ.

Рассмотрим первый режим работы СВЧ синтезатора частот, представленный на фиг. 3. Допустим, что частота f вх СВЧ входного СВЧ сигнала фиксирована и превышает f СЧ (как и в прототипе), а полоса перестройки СВЧ ГУН 1 (Δf ГУН) достаточна велика, например значительно превышает величину 2 f ПЧ. В этом случае при переходном процессе, предшествующем захвату частоты, на частотно-фазовый детектор 6 может попасть с выхода СВЧ смесителя 3 сигнал зеркальной частоты (в точке срыва синхронизации, в которой f ГУН =f 1 СЧ, где f 1 СЧ = f вх СВЧ +f ПЧ), что приведет к срыву синхронизации в петле ФАПЧ, переходу сигнала частоты f ГУН СВЧ ГУН в крайнее верхнее положение, соответствующее частоте f ГУН макс и, как следствие, к отказу в работе СВЧ синтезатора частот. Схема СВЧ синтезатора частот, выбранного в качестве прототипа, не предусматривает возможность выхода из этой ситуации. В предлагаемом СВЧ синтезаторе частот эта проблема решается следующим образом.

Фазовый компаратор 11 в режиме частотно-фазовой синхронизации (f ОП /m=f ПЧ /n, φ ОП =φ ПЧ) вырабатывает на своем выходе сигнал U ФК, соответствующий логической единице (лог. «1»). Этот выход фазового компаратора 11 соединен с входом ждущего мультивибратора 12, запуск которого осуществляется сигналом, соответствующим логическому нулю (лог. «0»). При входном сигнале, равном уровню лог. «0», первый 13 и второй 14 диоды закрыты и ждущий мультивибратор 12 не оказывает влияния на работу петли ФАПЧ. В том случае, когда режим фазовой синхронизации нарушается, на выходе фазового компаратора 11 возникает сигнал, соответствующий лог. «0». Это может происходить в моменты включения СВЧ синтезатора частот или при перестройке частоты f ОП опорного сигнала. Сигнал, соответствующий лог. «0» с выхода фазового компаратора 11 запускает ждущий мультивибратор 12 и на его прямом и инверсном выходах в течение длительности импульса τ м появляются уровни напряжений, равные соответственно лог.«1» и лог. «0» (то есть инверсные предыдущему состоянию), поэтому первый 13 и второй 14 диоды открываются и на первый и второй входы операционного усилителя 9 поступает дифференциальное напряжение, вызывающее появление начального (минимального) напряжения управления на выходе операционного усилителя 9, которое подается соответственно на управляющий частотой вход СВЧ ГУН 1, при этом устанавливается значение частоты СВЧ ГУН f ГУН =f ГУН мин. После окончания импульса ждущего мультивибратора 12 наступает пауза, равная величине Т М -τ м, где Т М - период повторения импульсов ждущего мультивибратора 12. В течение этой паузы петля ФАПЧ осуществляет перестройку частоты f ГУН сигнала СВЧ ГУН от минимального значения f ГУН мин до частоты, при которой происходит частотно-фазовая синхронизация (точка захвата частоты на фиг. 3). При перестройке частоты f ГУН сигнала СВЧ ГУН до значения, при котором f ГУН =f СЧ (где f СЧ =f вх СВЧ -f ПЧ) и при соблюдении условия f ГУН ≤f вх СВЧ (в соответствие с фазировкой ЧФД 6), устанавливается режим частотно-фазовой синхронизации, при котором f ОП /m=f ПЧ /n. На выходе фазового компаратора 11 возникает сигнал, соответствующий уровню лог. «1», переводящий мультивибратор 12 в ждущее состояние. Если по каким-либо причинам процесс синхронизации не произошел, то описанный цикл установления синхронизации в петле ФАПЧ повторяется. Необходимым условием захвата частоты, в данном случае, является то, что период повторения импульсов ждущего мультивибратора 12 должен соответствовать условию: Т М -τм>τ петли ФАПЧ, где

Т М - период повторения импульсов ждущего мультивибратора,

τ м - длительность импульса ждущего мультивибратора,

τ петли ФАПЧ - время установления синхронизации в петле ФАПЧ.

Рассмотрим второй режим работы СВЧ синтезатора частот, представленный на фиг. 4.

Предположим, что в начальный момент в СВЧ синтезаторе частоты выполняется условие частотно-фазовой синхронизации, при этом f вх СВЧ =f вх СВЧ1 . В этом случае частота выходного сигнала СВЧ синтезатора частот f СЧ =f СЧ·1 =f вх СВЧ1 -f ПЧ. Затем частота f вх СВЧ входного СВЧ сигнала быстро перестраивается в полосе Δf вх СВЧ перестройки входного СВЧ сигнала (как показано на фиг. 4) от значения f вх СВЧ1 к значению f вх СВЧ2 (при этом полоса перестройки частоты входного СВЧ сигнала Δf вх СВЧ составляет более 2 f ПЧ, где f ПЧ =f вх СВЧ -f ГУН. Одновременно с перестройкой частоты f вх СВЧ происходит перестройка частоты f ГУН СВЧ ГУН от значения f СЧ1 до значения f СЧ2 . Однако из-за инерционности петли ФАПЧ время перестройки частоты входного СВЧ сигнала (t пер.вх СВЧ) всегда меньше времени установления синхронизации в петле ФАПЧ (τ петли ФАПЧ), то есть t пер.вх СВЧ ≤τ петли ФАПЧ.

В результате инерционности петли ФАПЧ при перестройке частоты СВЧ ГУН также возникают условия для нарушения синхронизации. Так, например, как показано на фиг. 4, при перестройке частоты f ГУН от первоначального значения f СЧ1 (в верхней части диапазона перестройки частоты СВЧ ГУН) к следующему более низкому по частоте значению f СЧ2 . в СВЧ смесителе образуется сигнал зеркальной промежуточной частоты в точке, где f ГУН =f 1 СЧ2 =fвх СВЧ2 +f ПЧ. В этом случае (при заданной фазировке ЧФД 6) не будет соблюдаться условие f ГУН ≤f вх СВЧ, то есть не происходит захват частоты петлей ФАПЧ, что вызывает нарушение частотно-фазовой синхронизации с «затягиванием» частоты f ГУН в верхнее крайнее значение f ГУН макс диапазона перестройки частоты СВЧ ГУН. Для восстановления в петле ФАПЧ частотно-фазовой синхронизации в предлагаемом изобретении следует осуществить описанный в первом режиме работы СВЧ синтезатора частот цикл установления синхронизма. В схеме СВЧ синтезатора частот, выбранного в качестве прототипа, не предусмотрена возможность быстрого изменения частоты входного СВЧ сигнала, а следовательно, такая схема не позволяет осуществить устойчивую фазовую синхронизацию при перестройке частоты входного СВЧ сигнала.

Описанные выше режимы неустойчивой работы системы ФАПЧ в известном СВЧ синтезаторе частот, выбранном в качестве прототипа изобретения, были экспериментально проверены и подтверждены.

На основе предлагаемого изобретения разработаны и экспериментально опробованы образцы СВЧ синтезаторов частот, которые подтвердили устойчивую работу с быстрым временем восстановления частотно-фазовой синхронизации в различных режимах работы СВЧ синтезаторов частот - менее 100 мкс.

Источники информации

1. Манасевич В. Синтезаторы частот. Теория и проектирование. - М.: Связь, 1979 г.

2. Рыжков А.В., Попов В.Н. Синтезаторы частот в технике радиосвязи. - М.: Радио и связь, 1991 г., с. 110-113.

СВЧ синтезатор частот, содержащий СВЧ генератор, управляемый напряжением (ГУН), выход которого соединен с входом направленного ответвителя, первый выход которого является выходом СВЧ синтезатора частот, а второй выход направленного ответвителя соединен с первым входом СВЧ смесителя, второй вход СВЧ смесителя соединен с выходом источника входного СВЧ сигнала, выход СВЧ смесителя соединен с входом первого делителя частоты с переменным коэффициентом деления, выход которого соединен с первым входом частотно-фазового детектора, второй вход частотно-фазового детектора соединен с выходом второго делителя частоты с переменным коэффициентом деления, вход которого соединен с выходом источника опорного сигнала, а между частотно-фазовым детектором и СВЧ ГУН включен фильтр нижних частот, отличающийся тем, что СВЧ синтезатор частот дополнительно содержит фазовый компаратор, ждущий мультивибратор, два диода и операционный усилитель, при этом первый и второй выходы частотно-фазового детектора соединены соответственно с первым и вторым входами операционного усилителя, выход которого соединен с входом СВЧ ГУН, а фильтр нижних частот включен между первым входом операционного усилителя и его выходом, первый вход фазового компаратора соединен с выходом первого делителя частоты с переменным коэффициентом деления и первым входом частотно-фазового детектора, второй вход фазового компаратора соединен с выходом второго делителя частоты с переменным коэффициентом деления и со вторым входом частотно-фазового детектора, выход фазового компаратора соединен с входом ждущего мультивибратора, первый выход ждущего мультивибратора соединен через первый диод с первым выходом частотно-фазового детектора и с первым входом операционного усилителя, второй выход ждущего мультивибратора соединен через второй диод со вторым выходом частотно-фазового детектора и со вторым входом операционного усилителя, причем первый и второй диоды включены встречно друг другу, при этом СВЧ ГУН, направленный ответвитель, СВЧ смеситель, первый делитель частоты, частотно-фазовый детектор, операционный усилитель и фильтр нижних частот образуют петлю фазовой автоподстройки частоты (ФАПЧ) при условии: Т M -τ м >τ ФАПЧ, где Т М - период колебаний ждущего мультивибратора, τ м - длительность импульса ждущего мультивибратора, τ ФАПЧ - время установления синхронизации в петле фазовой автоподстройки частоты.

Похожие патенты:

Изобретение относится к технике связи. Технический результат заключается в комплексном улучшении основных параметров системы синхронизации, а именно: в повышении помехоустойчивости, в улучшении фильтрующих свойств системы, в расширении полос захвата и удержании синхронного режима работы, в уменьшении времени вхождения в синхронный режим работы, в обеспечении нулевой статической ошибки по фазе и в обеспечении корректной работы устройства в условиях наличия изменений и флуктуаций амплитуды входного сигнала или изменений коэффициента передачи фазовых детекторов.

Изобретение относится к частотной селекции и фильтрации радиосигналов. Технический результат заключается в обеспечении адаптации устройств селекции радиосигналов к помеховой обстановке, а также возможности управления их энергопотреблением.

Синтезатор частот с коммутируемыми трактами приведения частоты относится к радиотехнике и может быть использован для формирования сетки стабильных частот с равномерным шагом в приемных устройствах с повышенной помехозащищенностью, а также в приемопередающих устройствах с быстрой перестройкой рабочих частот.

Предлагаемый способ относится к технике связи и к режимам работы блоков синхронизации (БС), содержащим управляемые генераторы (УГ), точнее, к способам формирования высокостабильного выходного сигнала УГ БС в режиме удержания.

Изобретение относится к электронной технике, а именно к синтезаторам сетки частот (ССЧ) на базе контура импульсной фазовой автоподстройки частоты (ФАПЧ) с компенсацией помех дробности, и может применяться при использовании схем, основанных на амплитудно- или широтно-импульсной модуляции тока компенсации.

Изобретение относится к области радиотехники и автоматики, к системам автоматической подстройки частоты излучения газовых лазеров непрерывного действия с улучшенными стабилизационными характеристиками и может быть использовано в космической технологии, в частности, для измерения «фиолетового смещения» частоты лазерного излучения в гравитационном поле Земли.

Изобретение относится к электронно-вычислительной технике и радиотехнике. Технический результат заключается в повышении быстродействия и возможности формирования многочастотных частотно-модулированных сигналов. Цифровой вычислительный синтезатор частотно-модулированных сигналов содержит: эталонный генератор, блок формирования и задержки, три регистра памяти, четыре цифровых накопителя, делитель с переменным коэффициентом деления, два функциональных преобразователя код x - sin x, два инверсных фильтра sin х/х, коммутатор, два цифроаналоговых преобразователя. Цифровыми входами ЦВС ЧM сигналов являются входы первого, второго и третьего регистров памяти, а его аналоговыми выходами являются выходы первого и второго ЦАП. 2 ил.

Изобретение относится к области радиотехники. Tехнический результат - расширение полосы захвата путем изменения симметричной формы дискриминационной характеристики знакового логического фазового дискриминатора в асимметричную, а при увеличении зоны положительного или отрицательного знака дискриминационной характеристики увеличивается соответствующая односторонняя полоса захвата для начальных частотных расстроек соответствующего знака. Способ увеличения полосы захвата системы фазовой автоподстройки частоты с упомянутым дискриминатором характеризуется тем, что определяют знак разности входного и вырабатываемого управляемым генератором выходного колебаний, формируют управляющие напряжения, имеющие знак, соответствующий знаку разности фаз, которые объединяют в единый сигнал, которым управляют частотой управляемого генератора. 2 н.п. ф-лы, 7 ил.

Способ фазовой автоподстройки позволяет осуществлять синхронизацию от однофазного исходного сигнала с помехами. Технический результат заключается в улучшении практического быстродействия синхронизации до одного-двух периодов сигнала синхронизируемой частоты, фильтрации помех в формируемых сигналах синхронизированной фазы и частоты. В состав системы входят блоки фазовой фильтрации первого порядка, полосно-заграждающего фильтра второго порядка, фильтрации низкой частоты первого порядка, блока интегрирования, блока умножения, блока вычисления коэффициентов цифровых фильтров, четырехквадрантного арктангенса. Применение дискретных методов для физической реализации способа с привлечением микропроцессорных средств позволяет осуществить операции сравнения и вычисления нелинейных функций с приемлемыми точностью и вычислительными ресурсами. Фильтры реализуются с переменными коэффициентами, имеют первый и второй порядок. Благодаря относительно небольшой чувствительности фазового фильтра к изменению частоты возможно быстрое выделение опорной фазы из исходного сигнала. Применение дискретного интегратора с обратной связью по коэффициенту интегрирования позволяет осуществлять быстрый выход сигнала синхронизированной частоты на установившийся режим. Применение дискретного фильтра с изменяемыми коэффициентами и учета перехода фазы через граничные значения позволяет эффективно осуществлять фильтрацию синхронизированной фазы без ее смещения относительно фазы основной гармоники исходного сигнала. Данный способ позволяет строить на его основе системы управления по гармоническим составляющим в одно- и многофазных системах и симметричным составляющим в многофазных системах. Основное применение данного способа в управлении преобразовательной техникой, также возможно его использование для быстрой синхронизации в средствах связи и иных приложениях с требованиями высокого быстродействия по настройке на основную частоту и выделения опорной фазы. 1 ил.

Изобретение относится к области радиотехники и может быть использовано при организации систем связи с увеличенным количеством каналов, а также в измерительной технике, где требуется перестройка частоты с малым шагом. В основу изобретения поставлена задача получения микроволновых колебаний с малым шагом сетки частот, низким уровнем фазовых шумов и малым временем перестройки частоты. Для этого частоту опорного генератора, задающую частоту сравнения в фазовом детекторе синтезатора косвенного типа, выбирают в полосе ультракоротких волн. При этом частоту высокостабильного опорного генератора предварительно сдвигают на некоторую небольшую величину, задающую малый шаг сетки частот. Для чего сигнал опорного генератора подают на радиочастотный вход квадратурного модулятора, модулируемого низкочастотными квадратурными сигналами одинаковой частоты и амплитуды, но со сдвигом фаз 90°. Тогда частота сравнения отлична от частоты опорного генератора на значение частоты этих низкочастотных сигналов. Трансформированный по частоте сигнал с выхода квадратурного модулятора подают на первый вход частотно-фазового детектора. Частоту микроволнового генератора управляемого напряжением делят делителем с переменным коэффициентом, и подают на второй вход частотно-фазового детектора. С помощью фильтра нижних частот подавляют продукты сравнения переменного тока, а сигнал постоянного тока подают на вход микроволнового генератора управляемого напряжением. Такой способ позволяет формировать микроволновые колебания с шагом в единицы килогерц, при этом не повышая времени перестройки синтезатора, не повышая уровня фазовых шумов и сохраняя стабильность частоты синтезатора, определяемую стабильностью частоты опорного генератора, которая, например, достигает 10-7-10-8.

Изобретение относится к радиоэлектронике, в частности к синтезаторам частот на основе петли фазовой автоподстройки частоты (ФАПЧ). Технический результат заключается в снижении уровня фазовых шумов и побочных дискретных составляющих в спектре выходного сигнала, что в свою очередь повышает качество выходного сигнала, при сохранении высокого разрешения по частоте и широкой полосы перестройки. Синтезатор частот содержит соединенные последовательно умножитель частоты входного сигнала, делитель с фиксированным коэффициентом деления, первую микросхему прямого цифрового синтеза, фазочастотный детектор, первый фильтр низких частот, генератор, управляемый напряжением, контур отрицательной обратной связи, включающий в себя соединенные последовательно смеситель, один из входов которого соединен с выходом генератора, управляемого напряжением, а второй вход соединен с выходом умножителя частоты входного сигнала, второй фильтр низких частот и вторую микросхему прямого цифрового синтеза, выход которой соединен с входом фазочастотного детектора, и управляющее устройство, выходы которого соединены с входами первой и второй микросхем прямого цифрового синтеза. Изобретение обеспечивает снижение уровня фазовых шумов и дискретных составляющих в спектре выходного сигнала, что, в свою очередь, повышает качество выходного сигнала, при сохранении высокого разрешения по частоте и широкой полосы перестройки. 1 ил.

Изобретение относится к радиотехнике. Технический результат изобретения заключается в повышении быстродействия и возможности работы с опорным сигналом любой скважности, период которого кратен периоду тактов, а также возможность подстройки частоты тактов по фронтам принимаемых данных. Способ подстройки частоты, в котором на время действия импульсов на выходах фазового детектора (ФД) формируют сигналы положительной и отрицательной полярности соответственно, которые затем суммируют, фильтруют и полученным сигналом управляют частотой генератора, фронт импульса на первом выходе по фронту опорного сигнала, а его срез - по любому переключению тактов. Если фронт опорного сигнала появится позже фронта тактов, то также формируют сигнал на втором выходе ФД с длительностью паузы тактов. ФД содержит три элемента 2-И, три D-триггера и логическую схему конъюнкции 3-х сигналов. 2 н. и 7 з.п. ф-лы, 11 ил.

Изобретение относится к радиолокации и гидролокации. Технический результат – обеспечение подавления боковых лепестков для кода P3 нечетной длины. Для этого устройство подавления боковых лепестков при импульсном сжатии многофазных кодов Р3 содержит соединенные по входу модифицированный фильтр Woo для кода Р3 нечетной длины N и формирователь цифрового корректирующего сигнала из последовательно соединенных преобразователя кода в комплексно сопряженный код и цифрового фильтра с конечной импульсной характеристикой КИХ-фильтра порядка N+1 с (N+2) коэффициентами -1,1, 0,…0, -1,1, выходом соединенного с первым входом сумматора, линию задержки на длительность одного кодового элемента и двухвходовый вычитатель, где выход фильтра Woo подключен к входу линии задержки и к первому входу вычитателя, выходом соединенного со вторым входом сумматора, а второй вход вычитателя подключен к выходу линии задержки, первый коэффициент импульсной характеристики модифицированного фильтра Woo равен 1 - exp(iπ/N), где, а (N+2)-мерный вектор коэффициентов фильтра формирователя цифрового корректирующего сигнала соответственно равен -1,1, 0,0,…0, -1,1. 2 ил.

Предлагаемые устройства относятся к радиолокационным и гидролокационным системам с импульсным сжатием многофазных кодов. Технический результат заключается в повышении качества сжатия сигналов, производится подавление боковых лепестков, возникающих в процессе сжатия, при котором обеспечивается увеличение числа многофазных кодов длины N, для всех значений временных сдвигов (отсчетов), исключая двух ±N, в которых относительный уровень боковых лепестков находится в диапазоне от -20 lgN -6 до -20 lgN -8 dB за счет использования симметрично усеченных кодов, образованных последовательным удалением равного числа первых и последних символов кодов большей длины. При этом ширина главного лепестка на уровне -6 dB равна 2τ, на уровне PSL лежит в диапазоне 3÷4τ, а потери сигнал/шум на выходе устройства составляют -1.7 dB. Устройство подавления боковых лепестков при импульсном сжатии симметрично усеченных многофазных кодов длины N содержит соединенные по входу первый цифровой фильтр с КИХ порядка N-1 и формирователь цифрового корректирующего сигнала, состоящий из последовательно соединенных преобразователя кода в комплексно сопряженный код и второго цифрового фильтра с конечной импульсной характеристикой порядка N+1, выход которого соединен с первым входом сумматора, а выход первого цифрового фильтра подключен к линии задержки на длительность одного кодового элемента и к первому входу вычитателя, второй вход которого соединен с выходом линии задержки, а выход подключен ко второму входу сумматора. 3 н.п. ф-лы, 4 ил.

Группа изобретений относится к запоминающим устройствам и может быть использована для управления синхронизацией для записи в запоминающие устройства в несогласованной архитектуре. Техническим результатом является компенсация изменений задержки реальной сети распределения тактового сигнала. Устройство содержит схему приемника и схему кольцевого генератора. Схема приемника включает в себя путь передачи данных и сеть распределения тактового сигнала в несогласованной конфигурации. Схема кольцевого генератора включает в себя реплику сети распределения тактового сигнала, согласованную с реальной сетью распределения тактового сигнала. 3 н. и 17 з.п. ф-лы, 10 ил.

Генератор шкалы времени относится к устройствам синхронизации сигналов по частоте, сдвигу фазы и шкале времени. Техническим результатом является повышение точности синхронизации шкалы времени. Генератор шкалы времени содержит: блок приема шкалы времени, внутренний генератор квантовой последовательности, делитель, блок передачи шкалы времени, формирователь защитного интервала, временной селектор, блок переключаемых линий задержки, блок компараторов, генератор линейно-изменяющегося напряжения. 5 ил., 1 табл.

Изобретение относится к радиотехнике и может быть использовано в приемопередающих устройствах СВЧ диапазона частот. Техническим результатом является повышение устойчивой работы при перестройке частоты входного СВЧ сигнала. СВЧ синтезатор частот содержит СВЧ генератор, управляемый напряжением, направленный ответвитель, СВЧ смеситель, источник входного СВЧ сигнала, первый делитель частоты с переменным коэффициентом деления, частотно-фазовый детектор, второй делитель частоты с переменным коэффициентом деления, источник опорного сигнала, фильтр нижних частот, фазовый компаратор, ждущий мультивибратор, два диода и операционный усилитель. 4 ил.

Проблема стабильности частоты в приемопередающих устройствах существовала всегда. На относительно низких частотах (до 100-150 МГц) она решалась применением кварцевых резонаторов, на более высоких (400 МГц) – с помощью резонаторов на поверхностно-акустических волнах (ПАВ-резонаторах), для стабилизации же сверхвысоких частот часто применяют диэлектрические резонаторы из высокодобротной керамики или другие высокодобротные резонаторы . Описанные способы стабилизации с помощью пассивных компонентов имеют свои достоинства – простоту и сравнительную дешевизну реализации, но их главный недостаток – невозможность сколько-нибудь существенной перестройки частоты без смены частотозадающего элемента – резонатора. Невозможность быстрой электронной перестройки рабочей частоты при сохранении ее стабильности резко ограничивает применение радиоустройств, не позволяя, например, реализовать многоканальность.

Получившие в настоящее время широкое распространение интегральные синтезаторы частоты различных зарубежных фирм позволяют осуществить быструю электронную перестройку рабочей, в том числе и сверхвысокой, частоты, сохраняя при этом ее высокую стабильность. Такие синтезаторы частоты бывают прямого и косвенного типов . Достоинствами прямого синтеза относится высокое быстродействие при малом шаге сетки частот, но из-за необходимости фильтрации большого количества спектральных компонент, вызванных многочисленными нелинейными преобразованиями сигнала, в СВЧ схемах устройства прямого синтеза применяются редко . Для синтеза сверхвысоких частот обычно применяют синтезаторы косвенного типа, или синтезаторы с фазовой автоподстройкой частоты (ФАПЧ). Существует два основных типа интегральных синтезаторов с ФАПЧ – программируемые, значения частоты в которых задается внешним микроконтроллером по трехпроводной шине, и непрограммируемые, где коэффициенты деления внутренних делителей частоты фиксированы, а опорная частота задается внешним кварцевым резонатором. В простых СВЧ схемах обычно применяют непрограммируемые интегральные синтезаторы, например, MC12179 фирмы Motorola , к недостаткам которого следует отнести необходимость точного выбора кварцевого резонатора, что не всегда возможно. Программируемые синтезаторы частоты, например UMA1020М фирмы Philips, лишены этого недостатка, а поскольку в современных системах связи обязательно присутствует управляющий микроконтроллер, осуществить программирование такого синтезатора технически несложно. Автогенераторы сверхвысокочастотного диапазона используются в виде функционально законченных модулей, выполненных по гибридной технологии .

Примером применения описанных решений может служить простой лабораторный синтезатор сверхвысокой частоты, позволяющий с высокой точностью генерировать и стабилизировать частоту в диапазоне 1900 – 2275 МГц, предлагаемый в настоящей статье.

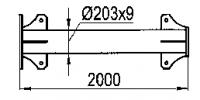

Структурная схема спроектированного синтезатора показана на рис. 1., внешний вид – на рис.2. Как видно их схемы, синтезатор состоит из управляемого напряжением генератора (ГУН или VCO) JTOS-2200 фирмы Mini-Circuits JTOS-2200, интегрального синтезатора частоты UMA-1020М и микроконтроллера Z86E0208PSC фирмы Zilog.

Сверхвысокочастотный сигнал, генерируемый ГУНом, поступает на выход лабораторного синтезатора и на вход главного программируемого делителя частоты, входящего в схему UMA-1020М.

Опорный сигнал, вырабатываемый кварцевым генератором JCO-8, поступает на вспомогательный программируемый частотный делитель, также входящий в схему UMA-1020М. Структурная схема UMA-1020М показана на рис. 3, подробную техническую документацию на UMA-1020М можно найти на сайте фирмы-производителя http://www.philips.de/ . Коэффициенты обоих делителей – главного и вспомогательного – устанавливаются микроконтроллером Z86E0208PSC по трехпроводной (данные DATA, синхронизация CLK и разрешение записи /ENABLE) шине. Структурная схема микроконтроллера Z86E0208PSC показана на рис. 4. Внутреннего ПЗУ микроконтроллера достаточно для программирования семи различных значений частот и одного тестового режима. Конкретные значения частот (или тестовый режим) устанавливаются перемычками на печатной плате лабораторного синтезатора. Перед загрузкой очередного значения частоты в интегральный синтезатор микроконтроллер опрашивает порт, подключенный к перемычкам, и, в соответствии с полученными данными, выбирает ту или иную прошивку. Новое значение частоты устанавливается автоматически при включении питания платы синтезатора. Алгоритм программирования синтезатора для микроконтроллера Z86E0208PSC показан на рис. 5, листинг программы приведен .

Более подробно о программировании микроконтроллеров фирмы Zilog можно прочитать в , полная техническая документация доступна на сайте http://www.zilog.com/ .

Особенностью применяемого ГУНа JTOS-2200 является диапазон напряжения настройки: от 0.5 до 5 Вольт. То есть, если значение напряжения настройки будет меньше 0.5 Вольт, фирма-производитель не гарантирует устойчивую генерацию колебаний. Проведенные эксперименты показали правдивость данного утверждения.

Принцип функционирования ФАПЧ, а также методика расчета фильтра обратной связи (Loop filter), довольно широко и неоднократно рассмотрены в технической литературе , поэтому в данной статье не рассматривается. Существует несколько бесплатно распространяемых программ, позволяющих рассчитывать параметры фильтров обратной связи, их можно найти в Интернете на http://www.analog.com/ или на www.national.com.

Для контроля правильности работы схемы синтезатора на плате установлен светодиод, свечение которого говорит об ошибке синтеза частоты. При корректной работе синтезатора светодиод гореть не должен, однако эта функция может быть отключена программно.

Себестоимость собранного лабораторного синтезатора не превышает 30 долларов. В качестве удешевления предлагаемого устройства можно предложить два пути: во-первых, можно объединить кварцевый источник опорных колебаний синтезатора и микроконтроллера, при этом надо помнить, что максимальная тактовая частота Z86E0208PSC составляет 8 МГц, в то время как для UMA-1020М она может быть в пределах 5-40 МГц. Во-вторых, ГУН можно разработать самостоятельно на транзисторах или усилительных интегральных микросхемах, используя методику, приведенную в .

Список использованной литературы

- Диэлектрические резонаторы/ М.Е. Ильченко, В.Ф. Взятышев, Л.Г. Гассанов и др.; Под ред. М.Е. Ильченко. – М.: Радио и связь, 1989. – 328 с.: ил. – ISBN 5-256-00217-1.

- Пестряков А.В. Интегральные схемы для устройств синтеза и стабилизации частот// Chip News. – 1996. - № 2.

- Лобов В., Стешенко В., Шахтарин Б. Цифровые синтезаторы прямого синтеза частот// Chip News. – 1997. - № 1.

- Wireless Semiconductor Solutions. Motorola. Device Data – Vol.1. DL 110/D, Rev 9.

- VCO Designer’s Handbook 2001. VCO/HB-01. Mini-Circuits.

- Гладштейн М.А. Микроконтроллеры семейства Z86 фирмы Zilog. Руководство программиста. - М.: ДОДЭКА, 1999, 96 с.

- The Z8 Application Note Handbook. Zilog. DB97Z8X0101.

- Стариков О. Метод ФАПЧ и принципы синтезирования высокочастотных сигналов//Chip News. – 2001. - № 6.

- Microwave Oscillator Design. Application Note A008// Hewlett-Packard Co. - publication number 5968-3628E (6/99)

- Shveshkeyev P. A VCO Design for WLAN Applications in the 2.4 to 2.5 GHz ISM Band//Applied Microwave&Wireless. – 2000. - №6. – P.100-115.